FPGA'larda Evrimsel Hesaplama: Programlamadan Evrime

Platformumuzdaki en çok okunan ve popüler makaleleri görmek için Trendler bölümüne geçebilirsiniz.

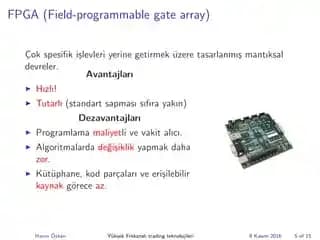

FPGA (Field Programmable Gate Array) teknolojisi, geleneksel olarak insan programcılar tarafından tasarlanıp yapılandırılan dijital devrelerin esnek bir şekilde uygulanmasını sağlar. Ancak 1990'ların sonlarında yapılan deneysel çalışmalar, FPGA'ların programlama yerine rastgelelik ve evrimsel algoritmalar yoluyla kendi kendine istenen işlevi gerçekleştirecek şekilde evrilebileceğini göstermiştir. Bu yaklaşım, klasik programlama paradigmasının dışına çıkarak, donanımın kendi yapısını optimize etmesini ve yeni çözümler üretmesini hedefler.

Evrimsel Hesaplama ve FPGA

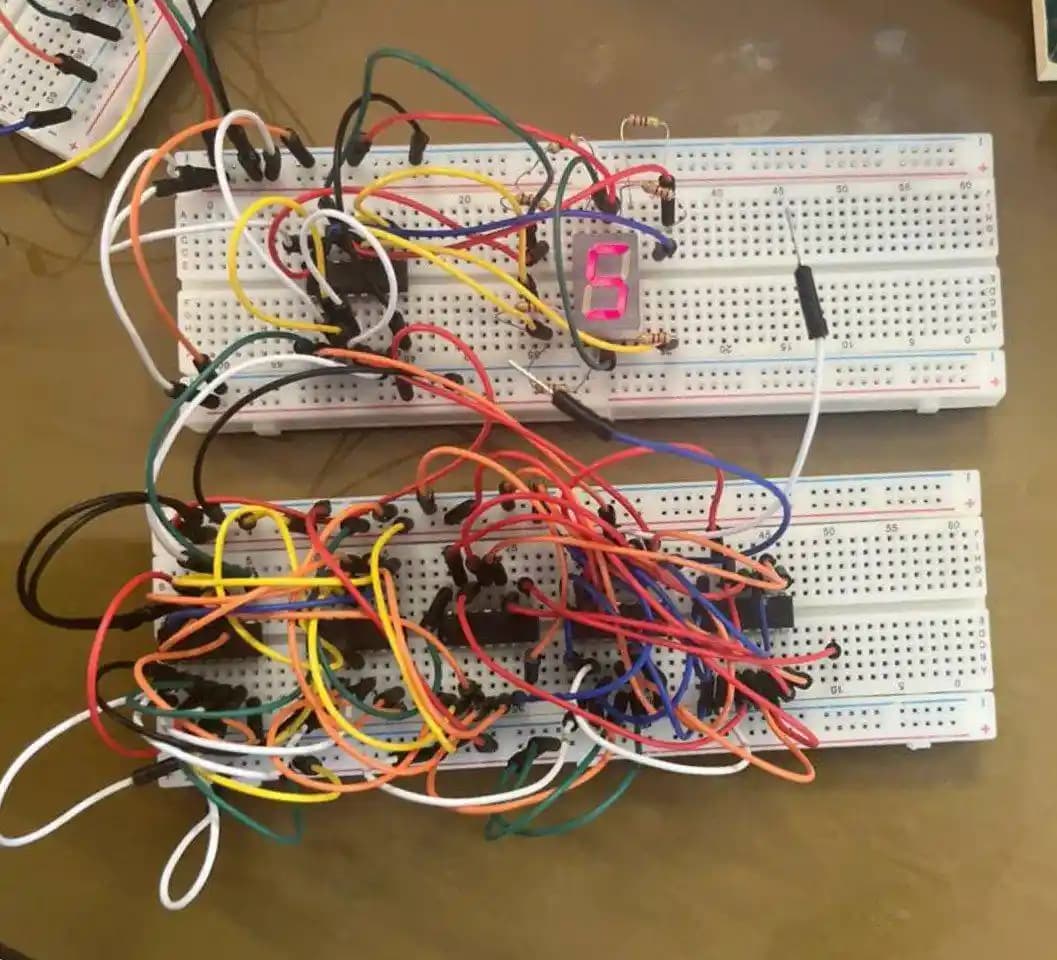

Evrimsel hesaplama, biyolojik evrim prensiplerinden esinlenen bir algoritma ailesidir. Bu algoritmalar, rastgele mutasyonlar, seçilim ve çaprazlama gibi mekanizmalarla çözüm adaylarını iteratif olarak geliştirir. FPGA üzerinde uygulandığında, devre yapısı ve bağlantıları rastgele değiştirilir, performans testleriyle değerlendirilen varyantlar arasından en iyi olanlar seçilir ve sonraki nesillere aktarılır. Böylece, binlerce nesil sonunda istenen işlevi yerine getiren bir donanım konfigürasyonu ortaya çıkar.

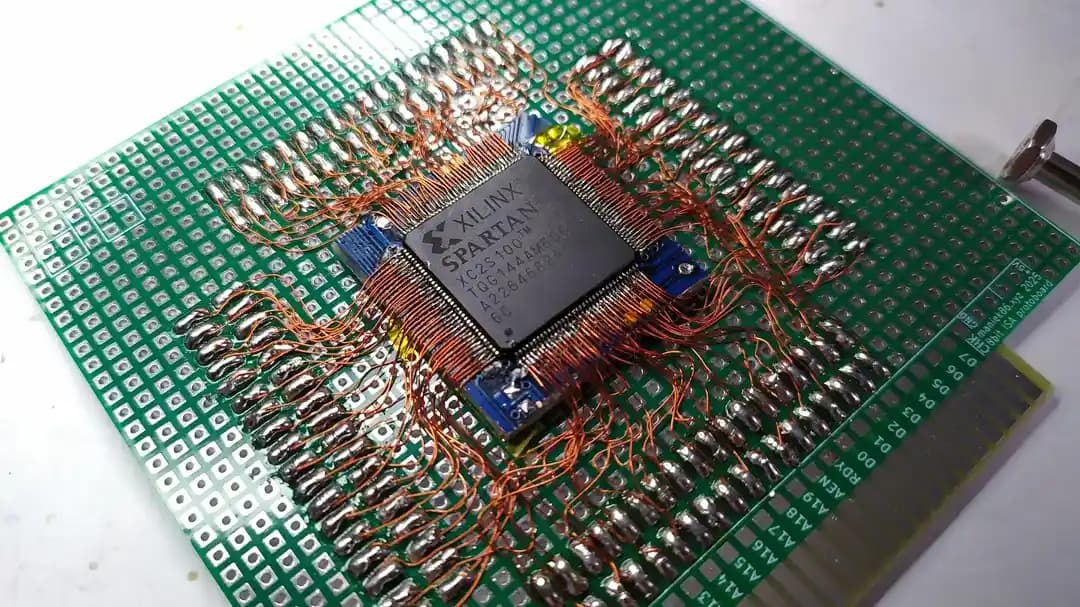

1996 yılında Adrian Thompson tarafından gerçekleştirilen deneyde, klasik programlama yapılmadan, FPGA'nın yapılandırması 4000 nesil boyunca evrimsel algoritmalarla değiştirildi. Sonuçta, FPGA kendi kendine belirli bir ses sinyalini ayırt eden bir devreye dönüştü. İlginç olan, devrenin bazı kısımlarının görünürde işlevsiz olduğu halde çıkarıldığında devrenin çalışmayı durdurmasıydı. Bu durum, devrenin analog ve elektromanyetik etkilerle karmaşık bir şekilde etkileşim halinde olduğunu gösterdi.

Ayrıca Bakınız

Sınırlamalar ve Zorluklar

Evrimsel olarak elde edilen FPGA konfigürasyonlarının en önemli dezavantajlarından biri, bu yapıların sadece orijinal FPGA üzerinde çalışmasıdır. Yani, aynı tasarım başka bir FPGA üzerinde aynı şekilde işlemez. Bunun nedeni, devrenin çalışmasının çip içindeki fiziksel ve elektriksel etkilerle bağlantılı olmasıdır. Bu durum, dijital devre tasarımında genellikle kaçınılan bir durumdur çünkü tekrarlanabilirlik ve güvenilirlik kritik öneme sahiptir.

Ayrıca, evrimsel algoritmalarla elde edilen çözümler genellikle laboratuvar ortamında minimum gereksinimleri karşılayacak şekilde optimize edilir. Uzun vadeli güvenilirlik, hata toleransı ve performans garantisi sağlamak zordur. Bu nedenle, uzay aracı, tıbbi cihaz veya otomotiv gibi kritik uygulamalarda insan mühendislerin tasarımı ve kapsamlı testler tercih edilir.

FPGA ve ASIC Karşılaştırması

Bazı kaynaklarda FPGA'ların ASIC'lerden (Application-Specific Integrated Circuit) daha yavaş ve sıcak çalıştığı iddia edilse de, bu genellikle doğru değildir. FPGA'lar, ASIC'lere göre esnek olmaları nedeniyle tercih edilirken, performans açısından ASIC'ler genellikle daha hızlı ve daha az güç tüketir. FPGA'lar, belirli görevlerde mikrodenetleyicilere göre daha hızlı ve daha soğuk çalışabilir ancak ASIC'ler genel olarak en yüksek performans ve verimlilik sunar.

Günümüzde Evrimsel Hesaplama ve Yapay Zeka

Son yıllarda, evrimsel hesaplama ve genetik algoritmalar, yapay zeka ve makine öğrenmesi alanlarıyla birleşerek yeni tasarım yöntemlerine ilham vermektedir. Özellikle jeneratif karşıt ağlar (GAN) gibi yapılar, evrimsel adaptasyon prensiplerine benzer şekilde çalışır. Bu yöntemlerde, çözümler sürekli olarak değerlendirilir, geliştirilir ve daha iyi performans için optimize edilir.

Ayrıca, yapay zeka destekli HDL (Hardware Description Language) tasarım araçları, VHDL veya Verilog kodlarının analizinde ve iyileştirilmesinde kullanılmaktadır. Bu araçlar, insan mühendislerin tasarım sürecini hızlandırmak ve hataları azaltmak için destek sağlar.

Geleceğe Bakış

Evrimsel algoritmaların FPGA üzerinde uygulanması, donanım tasarımında yeni keşiflere ve yaratıcı çözümlere kapı aralayabilir. Ancak mevcut zorluklar nedeniyle bu yöntem, insan mühendislerin yerini almak yerine, onların yanında bir araştırma ve geliştirme aracı olarak değerlendirilmektedir. Ayrıca, farklı yapay zeka sistemlerinin işbirliği ve kendi kendini geliştiren algoritmaların entegrasyonu, makine bilincine benzer yeni türde zeki makinelerin geliştirilmesine olanak sağlayabilir.

"Evrimsel algoritmalar, devre tasarımında yeni yöntemler keşfetmek için bir başlangıç noktası olabilir ancak güvenilirlik ve tekrarlanabilirlik gibi kritik kriterler için henüz insan mühendislerin deneyimi gereklidir."

Sonuç olarak, FPGA'ların evrimsel algoritmalarla yapılandırılması, donanım tasarımında yenilikçi bir yaklaşım olarak önem taşır ancak pratik uygulamalarda sınırlamaları ve riskleri göz önünde bulundurulmalıdır.